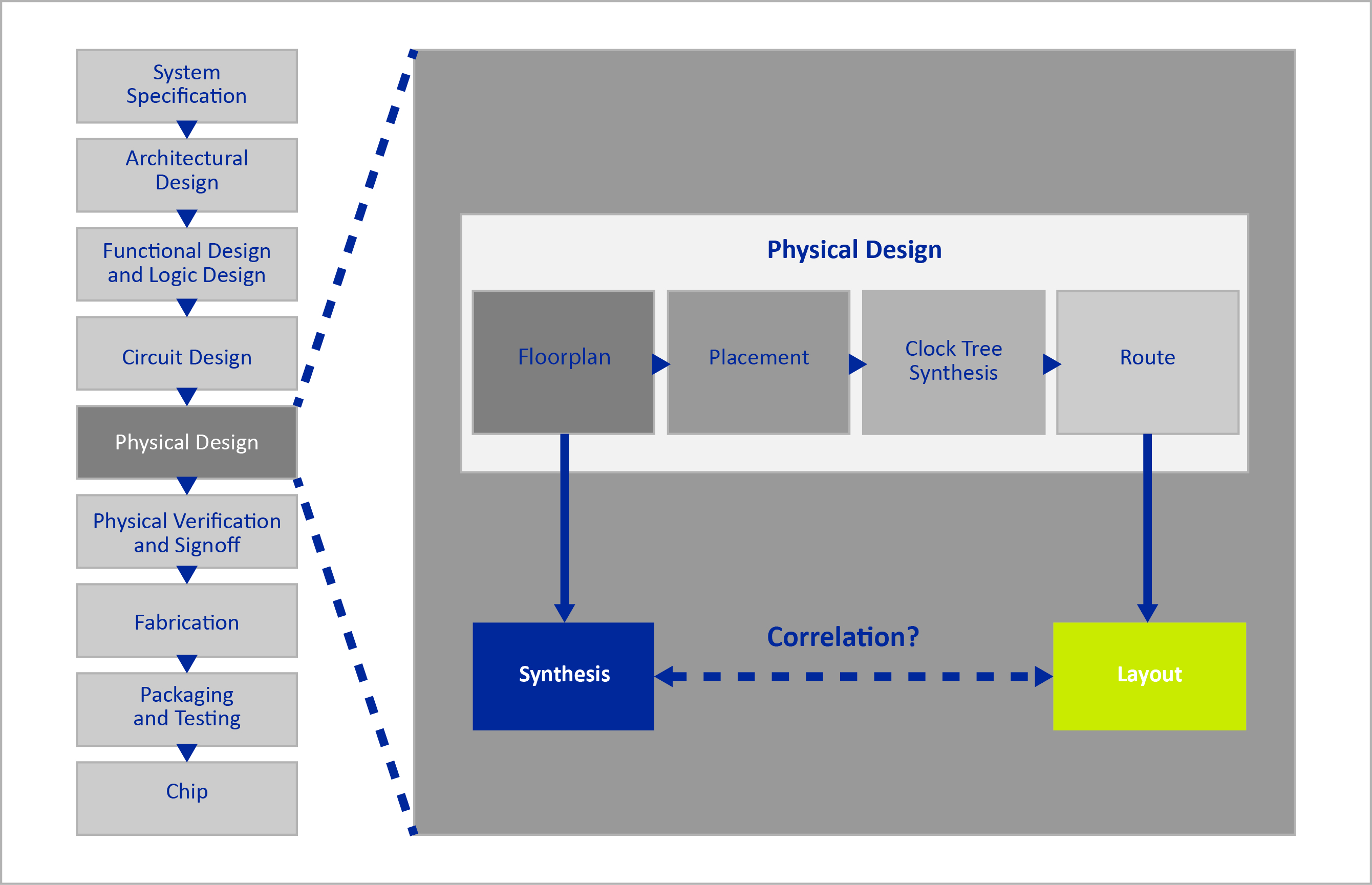

In theory, physical synthesis tools have all the necessary information about the layout; in practice, they must be correlated very carefully to real-world layout data.

The design of a chip involves many stages, from system specification and architectural design, all the way to the fabrication and packaging of the final silicon that goes into a device. During this cycle, it is crucial to have reliable estimates of timing and area in order to plan properly and meet expectations.

Read the full article published on EETimes.

The Article will take a look into the physical design (or backend design) portion of the process; specifically, at the correlation of timing and area within the steps associated with the physical design.

You might also like

More from Deep Learning

Bringing Power Efficiency to TinyML, ML-DSP and Deep Learning Workloads

In recent times, the need for real-time decision making, reduced data throughput, and privacy concerns, has moved a substantial portion …

Human Presence Detection and You

Mobile phones and tablets are getting more powerful, but if you’re serious about doing work (remotely), the dedicated work laptop …

Meeting the challenges of edge AI

AI is becoming an increasingly popular technology, finding uses in more and more applications in sectors such as automotive, vision …