Overview

The CEVA-X2™ is an advanced DSP optimized for intensive sound processing applications. It has been specifically designed to tackle multi-microphone speech processing use-cases, high quality audio playback and post-processing, and embedded sound neural network implementations.

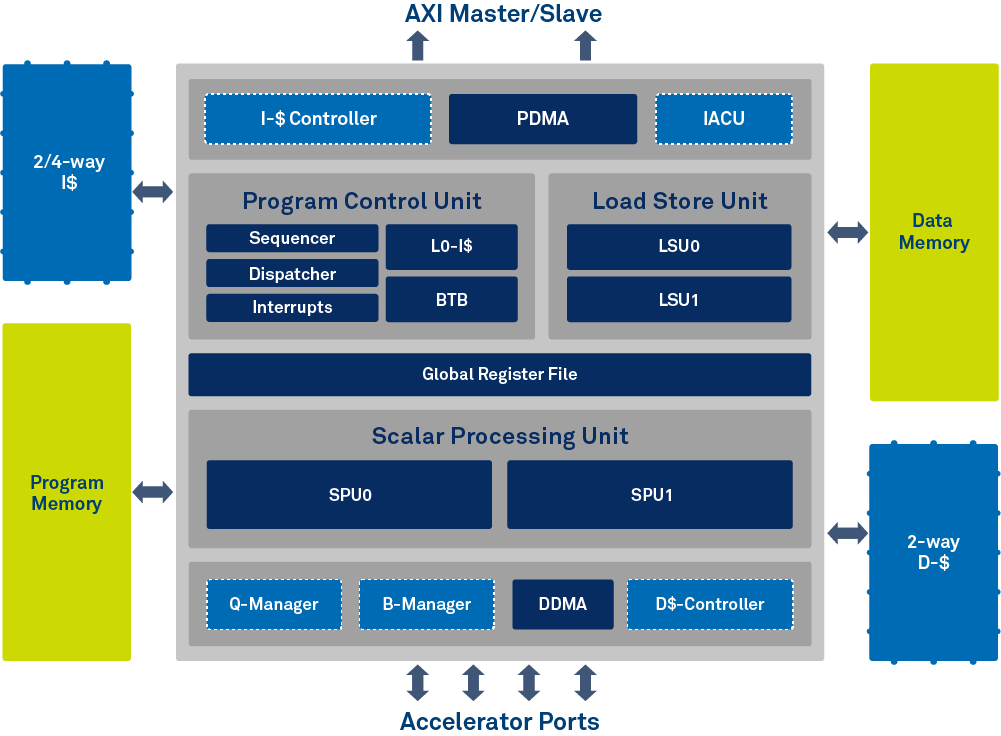

The CEVA-X2 is a combined DSP/controller based on a VLIW/SIMD architecture with a 10-stage pipeline, operating at 2GHz in typical conditions of a 16nm process.

Other key features include:

- 4.5 CoreMark/MHz score,

- dual 32×32 MAC operations per cycle,

- quad 16×16 MAC operations per cycle,

- 64-bit SIMD fixed-point operations,

- Up to two IEEE single-precision floating-point units operating in parallel.

The processor includes two Scalar Processing Units (SPUs), which support 8/16/32/64-bit data types for arithmetic and logic operations. It supports both static branch prediction and optional dynamic branch prediction, and offers both supervisor and user modes.

At a system level, the CEVA-X2 includes a 2-way or 4-way set-associative data cache with write-through and write-back policies, as well as hardware and software pre-fetch capabilities.

Data traffic is managed by the CEVA-X2 optional CEVA-Connect mechanism, which ensures intelligent scheduling for high Quality of Service (QoS) and low latency data transfer tasks and minimizes CEVA-X2 processor load.

CEVA-X2 supports your audio/voice/speech software needs using the extensive CEVA Sound Library, CEVA Neural Network Library, CEVA’s ClearVox Voice processing software package, and a vast ecosystem partner offerings of software solutions for any sound application.

Benefits

A fully featured VLIW/SIMD architecture optimized for the most demanding DSP algorithms

Main Features

- Parallel DSP with two SPUs (Scaler Processing Units)

- Flexible data plane processing with 8/16/32/64-bit native C data types support

- Highly efficient controller with a 4.5 CoreMark/MHz score

- Advanced Instruction and Data cache architecture with ACE coherency support

Block Diagram