High Level Programmable, Modern Processor Digital Signal Controller

for a Broad Range of Signal Processing and Control Workloads

Ceva-BX1 is a multipurpose hybrid DSP and digital signal controller designed for the inherent low power requirements of DSP kernels with high-level programming and compact code size requirements of a large control code base.

Using dual 32X32-bit MAC and quad 16X16-bit MACs, the Ceva-BX1 serves low to mid-range DSP workloads, such as cellular IoT, protocol stacks, light AI processing and always-on sensor fusion, with up to 8 GMACs per second. The Ceva-BX1 is using an 11-stage pipeline and 4-way VLIW micro-architecture, it offers parallel processing with a scalar compute engine, load/store and program control that reaches a speed of 2 GHz at a TSMC 7nm process node using common standard cells and memory compilers.

The Ceva-BX1 digital signal controller Instruction Set Architecture (ISA) incorporates support for Single Instruction Multiple Data (SIMD), as well as half, single and double precision floating point units for high accuracy sensor fusion and positioning algorithms.

Security is addressed using dedicated trusted execution modes to comply with the stringent safety standards.

The Ceva-BX1 is accompanied by a comprehensive software development tool chain, including:

- Advanced LLVM compiler

- Eclipse based debugger

- DSP and neural network compute libraries

- Neural network frameworks support

- Real Time Operating Systems (RTOS)

Benefits

Ceva-BX1 digital signal controller combines low power DSP kernels execution with powerful control capabilities and compact code size

Main Features

- Quad 16x16 MACs

- Dual 32x32 MACs

- 4-way VLIW

- 8/16/32/64-bit data types

- 16x8 and 8x8 Neural Network support

- Half, single and double precision IEEE floating point units

- Innovative Branch Target Buffer minimizing branch overhead

- Hardware loop buffer for reduced power consumption of code loops

- High performance controller

- 4 CoreMark/MHz

- Dynamic branch prediction

- Full RTOS support

- Secured execution modes

- Compact code size

- Advance system control

- Automatic Queue and Buffer management mechanisms to integrate co-processors and create a cluster of Ceva-BX cores

- Dedicated HW accelerator ports

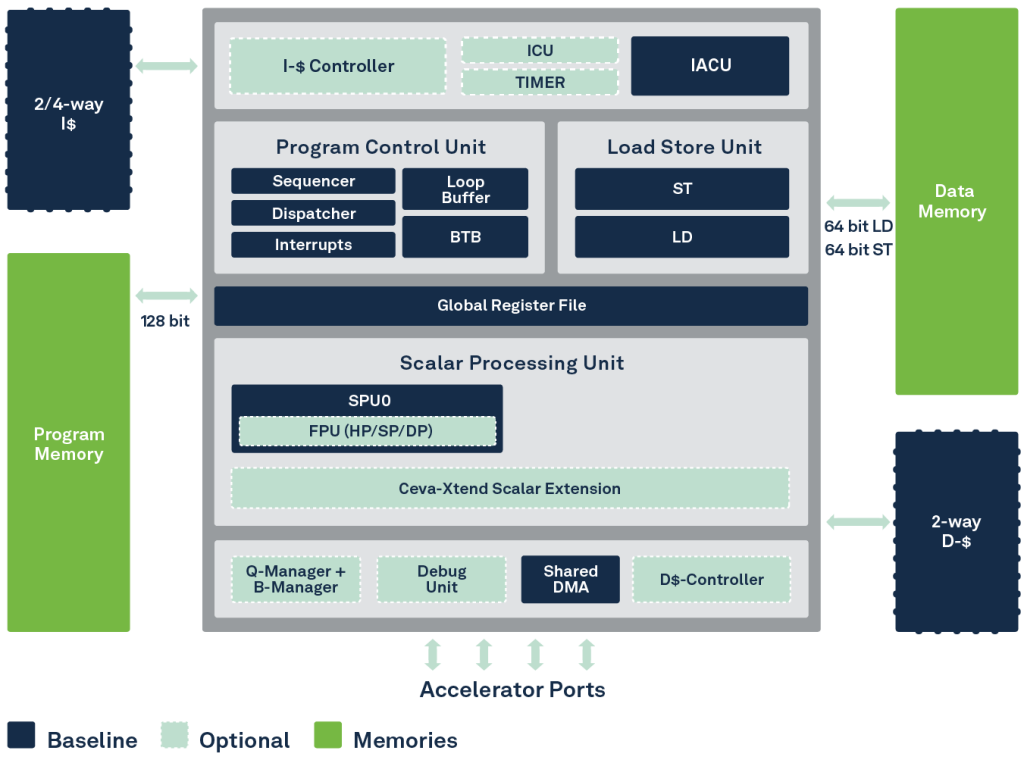

Block Diagram