www.ceva-dsp.com

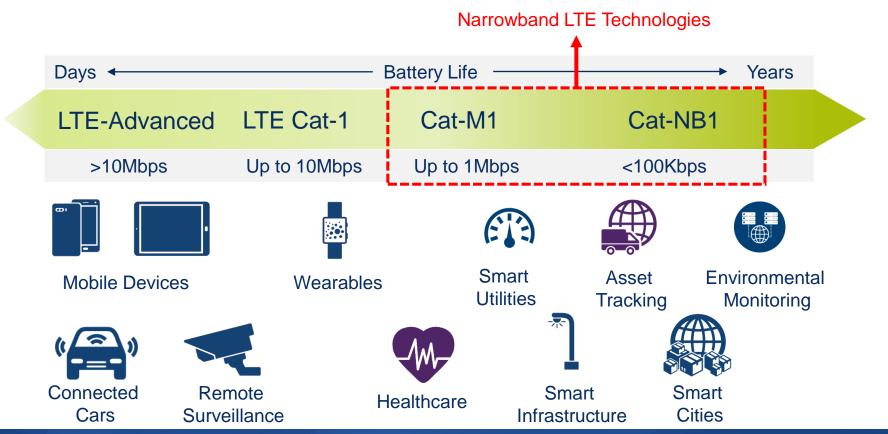

## Cellular IoT for The Massive Internet of Things

# Introducing the CEVA-X1

Lightweight, multi-purpose, single-core processor for cellular IoT

- Derived from the NEW CEVA-X Architecture Framework

- Extended Instruction Set Architecture (ISA) combining DSP+CPU processing

- Eliminates need for separate CPU

- Addresses severe size, power and cost limitations for cellular IoT devices

- Comes with dedicated Cat-NB1 instructions to vastly improve performance

DSP+CPU

30% Reduced Power

Multi Mode

# Introducing the CEVA-X1 (cont'd)

Also serves as processing hub for other closely-related IoT technologies

#### Connectivity

Short and long range wireless

### Positioning

GNSS and indoor positioning

### Sensing

Sensor-fusion using motion, sound and ambient sensing

#### Voice

IoT related voice activation and narrowband voice communication

## The Three Pillars of CEVA-X1

- Powerful DSP Processing

- 4-way VLIW Architecture

- ▶ 32-bit SIMD operations

- ▶ 64-bit memory bandwidth

- 2x 16x16 or 1x 32x32 MAC

- ► IEEE Single-Precision Floating Point

- Efficient Controller Capabilities

- CoreMark/MHz: 3.3

- On par with ARM Cortex-M4

- Compact code size

- ► Full RTOS support

- Ultra-fast context switch

- Comprehensive Control code ISA:

- Zero latency

- Byte support

- Dynamic and static branch prediction

- Advanced System Control

- CEVA Connect

- Offload the processor with control and data plane hardware

- Automatic data traffic management

- for data flow between PHY and HWA

- Dedicated interfaces to connect multiple HW accelerators

- Supports both AHB and AXI interconnect

Effectively combines strong and native DSP capabilities with advanced real-time Controller attributes

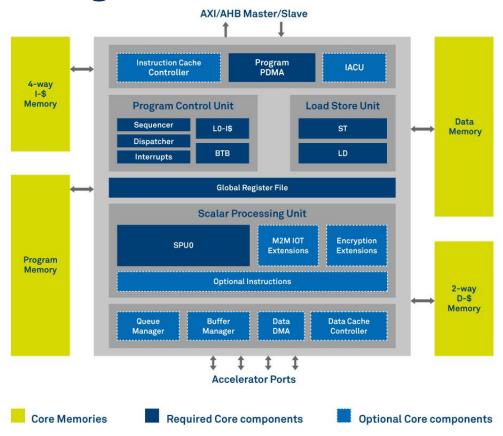

# **CEVA-X1 Architecture Diagram**

| Features                  | Configurations |

|---------------------------|----------------|

| Pipeline                  | 10 stage       |

| VLIW                      | 4 way          |

| SIMD [bit]                | 32             |

| Scalar Units              | 1              |

| MAC [16x16-bit]           | 2              |

| MAC [32x32-bit]           | 1              |

| Data Memory width [bit]   | 64 LD + 64 ST  |

| SP Floating-Point         | Optional       |

| Dynamic Branch Prediction | Optional       |

| Data Cache                | Optional       |

| Instruction Cache         | Optional       |

| CEVA-Connect              | Optional       |

## **Dedicated Cat-NB1 Instructions**

CEVA

- ▶ Detailed analysis of the Cat-NB1 standard and profiling of Baseband and Layer 2 (MAC, PDCP, RLC) on CEVA-X1

- Low data-rate cellular IoT standards are better addressed with dedicated instructions rather than HW accelerators external to the core

- Baseband: Viterbi, Turbo encoder

- Layer 2: Encryption

- CEVA-X1 Power Savings Unit (PSU) supports LTE Cat-M1 and Cat-NB1 PSM and eDRX modes to reduce power consumption further during idle and sleep time

Reduces the power consumption of the Cat-NB1 modem, excluding RF, by a further 30%.

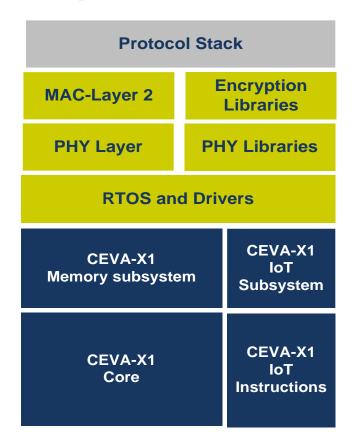

# **CEVA-X1 HW and SW Components**

## ► SW components

- RTOS and Drivers

- Cat-NB1 and Cat-M1 PHY Libraries

- ► Encryption Libraries

- MACs & Protocol Stacks

- From CEVA & Partners

## ► HW components

- Cat-M1 and Cat-NB1 instructions

- Baseband and Encryption

- ▶ IoT subsystem

- Standard specific HW accelerators

- e.g. Cat-M1 Turbo decoder

- Peripherals and interfaces

## **Smart Watch Multi-mode Use Case**

### Wearalone Smartwatch

- Samsung Gear S3

- Your Smartphone is no longer necessary!

WiFi 802.11n

Bluetooth 4.1

GPS

Voice

Cat-M1

Sensors

### Multi-mode Use Case

- True concurrent multi-mode is required for

- ► Communication: LTE Cat-M1, Wi-Fi, BLE

- Only one will run at a given time

- ▶ IoT: GNSS, Sensors, Voice codec & trigger

- May all run at the same time

- Cat-M1 and GNSS don't have to run at the same time

- They are often idle and can time share Processor workload

A single CEVA-X1 can handle all above workloads concurrently, running everything in software

# **CEVA-X1** Putting it all together

- Coremark/MHz: 3.3

- Dynamic Branch Prediction

- ► Full RTOS Support

- Ultra Fast Context Switch

DSP+CPU in a single Core

Multipurpose processor

- Smart Home

- Asset Trackers

- Smart City, Smart Plants

- Smart Farming

- Wearables, eHealth

Standard Specific Instructions

Standard Specific Accelerators HW and SW

Optimized SW PHY Libraries

MACs and Protocol stacks

Cellular IoT

Standard Specific

HW and SW

Multi-mode ideal for IoT

- Wi-Fi, Bluetooth, BLE

- Zigbee / Thread

- SNSS: GPS, Beidou, Glonass

- Indoor positioning: beacons

- Sensors

- Vocoder, voice activation

**CEVA**