SLAM SDK, vision libraries, RTOS and drivers for SensPro sensor hub DSPs and NeuPro AI processors

The Application Developer Kit (ADK) for Ceva-XM, SensPro2 and NeuPro streamlines the...

Intelligent imaging and vision processor for low-power embedded systems

The Ceva-XM4 imaging and computer vision processor IP solves the most critical issues for the development of energy-efficient embedded vision systems where die size and power budget are extremely constrained, yet algorithms require intensive processing.

The Ceva-XM4 vision DSP and its associated tools and libraries combine to deliver a comprehensive vision IP platform that allows developers to simply and easily address the key elements of intelligent vision processing, namely 3D vision, computational photography, visual perception, and analytics.

Choosing the Ceva-XM4 opens up a new world of possibilities for the designer, including running computer vision on video streams (1080p, 4K), combining depth generation with vision processing, enabling multi-application processing (for example, combining gesture, face detection, emotions, eye-tracking, and depth), and implementing multi-image algorithms in high resolution.

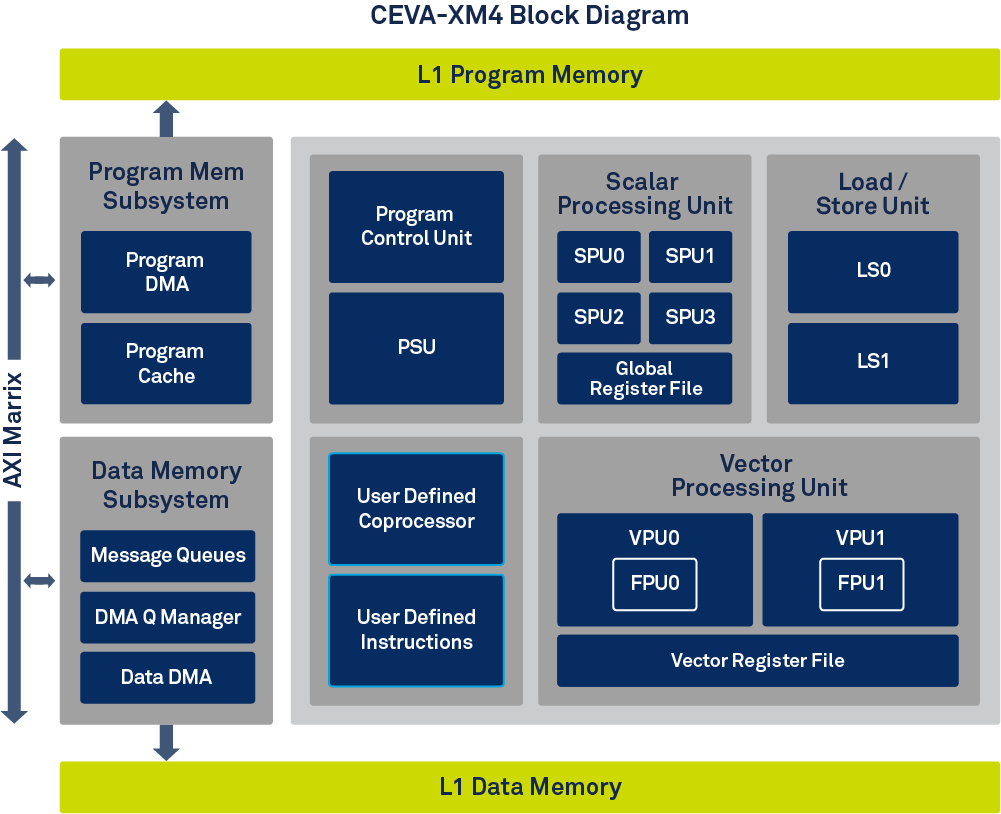

Fully programmable in high-level languages, the Ceva-XM4 is an extremely high-performance, low-power, fully synthesizable DSP and memory subsystem IP core. It incorporates a wide-vector architecture with fixed- and floating-point processing, multiple simultaneous scalar units, and a vision-oriented, low-power instruction set, making it an ideal imaging and computer vison processor for low-power embedded systems.

Benefits

The CEVA-XM4 offers faster processing, lower energy consumption, and smaller die size compared to GPU-based solutions. More than just a vision processor, the CEVA-XM4 provides a complete development platform with extensive vision libraries that offload computer vision from the host CPU to achieve significant performance boost and energy savings.

Fully programmable using high-level languages

Enables computationally demanding imaging and vision algorithms with low power

Complete vision IP platform to enable OEM product differentiation

Main Features

- Programmable vector-processing DSP based on a dedicated pixel-processing VLIW/SIMD architecture

- Fourteen-stage pipeline with nine functional units that can work in parallel

- Support for both fixed-point and floating-point computations

- Dedicated interface ports for hardware accelerators connectivity

Enabling mass market ADAS applications using real-time vision systems

Inside the NextChip APACHE4 and CEVA-XM4 affordable embedded platform

As the automotive market experiences accelerated growth and rapid adoption of vision applications such as Camera Monitoring Systems, Smart Rear Cameras, and Driver Monitoring Systems, there is a need for solutions that are both efficient and cost effective to address these applications in high volumes. In addition, these solutions must also allow for Tier-1s to both differentiate and meet the growing demands in performance from today’s OEMs.