Industry’s Most Comprehensive 5G Baseband Platform IP for Mobile Broadband and IoT

Ceva-PentaG2 is Ceva’s second generation 5G NR baseband modem IP platform. It is the industry’s only...

Highly powerful and scalable multi-mode communication processor for advanced wireless applications

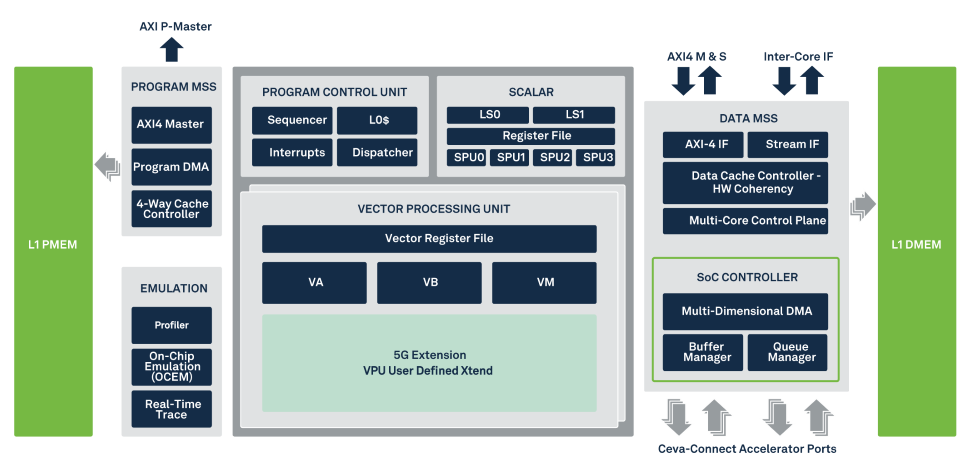

The Ceva-XC4500 DSP vector communication processor is the fourth generation of the widely licensed Ceva-XC™ architecture. Optimized for advanced communication applications, and especially high-performance wireless infrastructure equipment, it features a combination of VLIW and vector engines that enhance typical DSP capabilities with advanced scalar and floating-point vector processing.

Based on the architecture of the Ceva-XC4000 DSP family, the Ceva-XC4500 DSP core has two advanced VPUs that support both fixed-point and floating-point instruction sets. Built-in support for traffic management and dynamic scheduling provide efficient data processing within base stations, remote radio heads, and backhaul equipment. Supported by full hardware cache coherency, multiple cores can be deployed to scale the amount of traffic to be handled, from picocells to macrocells to Cloud-RAN, with no software overhead.

With its innovative programmable approach, the Ceva-XC4500 offers the high flexibility required to support a large number of wireless standards on a single programmable platform, which significantly reduces development cost and time-to-market.

Benefits

Provides an extensive instruction set optimized for a wide range of communications standards, enabling rapid implementation of software modems with a minimum of hardware

Modem design with minimal hardware requirements

Optimized for wireless applications in the high-end smartphone and eNode segments

Ceva-Connect schedules data transfers to hardware accelerators and peripherals, which frees the communication processor for higher-level tasks

Main Features

- Two Vector Processing Units (VPU)

- Extremely powerful computation capabilities

- Scalable and configurable architecture

- Innovative second-generation PSU

- Complete memory subsystem with cache-coherent instruction and data caches

Block Diagram