High Level Programmable, Modern Processor Digital Signal Controller

for a Broad Range of Signal Processing and Control Workloads

Ceva-BX1 is a multipurpose hybrid DSP and digital signal...

Overview

The CEVA-X1™ is a multi-purpose combined DSP and control processor aimed at multi-mode IoT hub devices for handling cellular, LPWA, short range communication, positioning, always-on sensor-fusion, and speech processing concurrently.

The CEVA-X1 is ideal for M2M protocol stack and baseband PHY control, including LTE Cat-NB1, Cat-M1, Sigfox, LoRa, Wi-Fi 802.11n, 802.11ah, Bluetooth, Bluetooth Low Energy, and Zigbee/Thread. It also supports positioning and motion-sensing functions, including GNSS (GPS, Beidou, GLONASS, Galileo), fusion of multiple indoor positioning and activity sensors, voice activation, and sound processing.

The CEVA-X1 has been specifically designed as a single core IoT hub solution with dedicated instructions to optimize overall system power, performance, and chip area for baseband channel coding/decoding functions, as well as fusion of multiple always-on sensors. Thanks to these optimizations, 5- to 10-year single battery operation at a very low cost is easily achievable.

Control performance has been optimized on the CEVA-X1 for efficient protocol stack execution and reaches 3.6 CoreMark/MHz, which exceeds the most popular IoT CPUs on the market today.

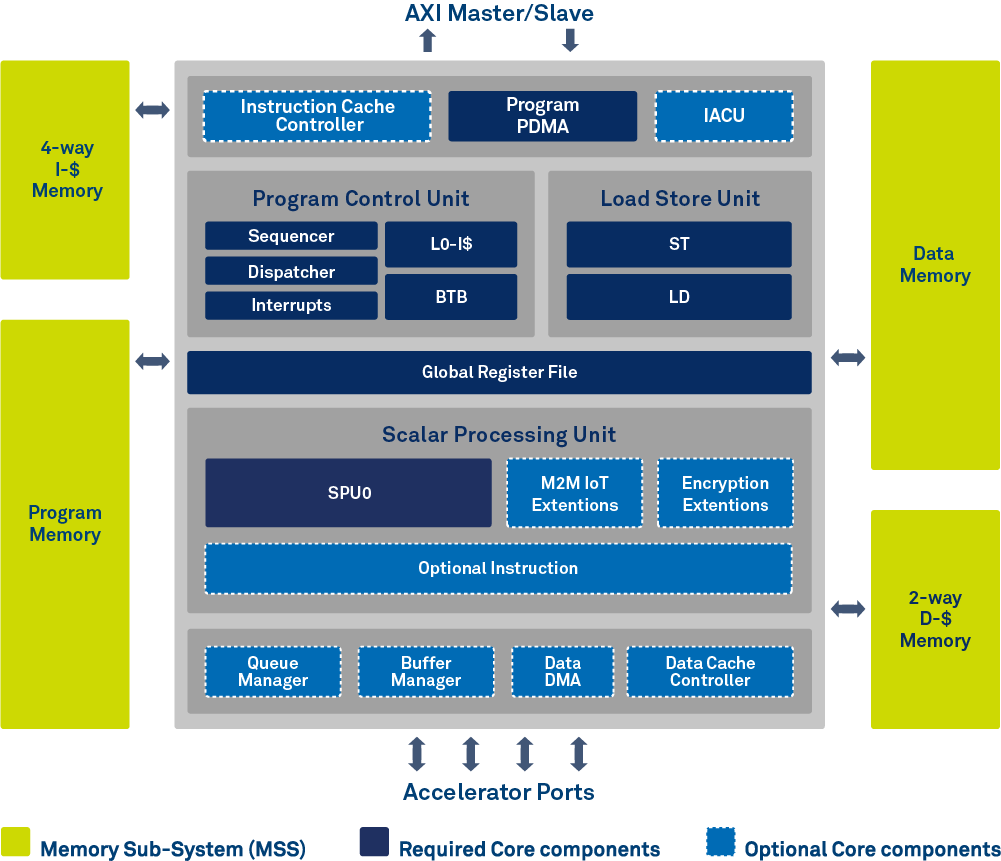

The CEVA-X1 architecture and C compiler natively support RTOS features, ultra-fast context switches, 8/16/32/64-bit data types, supervisor and user modes, dynamic branch prediction, as well as instruction and data caches.

Benefits

Offers extremely flexible, low-power operation across a very wide range of multi-mode use cases including asset trackers, geo-fencing, wear-alone devices and always-on applications

Easily applied to a wide range of IoT applications

Compact and efficient single core solution

Highly scalable application-specific instruction set

Main Features

- Unified DSP/Controller with a single SPU

- Flexible VLIW/SIMD architecture with a compact code size

- Highly efficient controller with a 3.6 CoreMark/MHz score